Figure 2 from A Study of Snapback and Parasitic Bipolar Action for ESD NMOS Modeling | Semantic Scholar

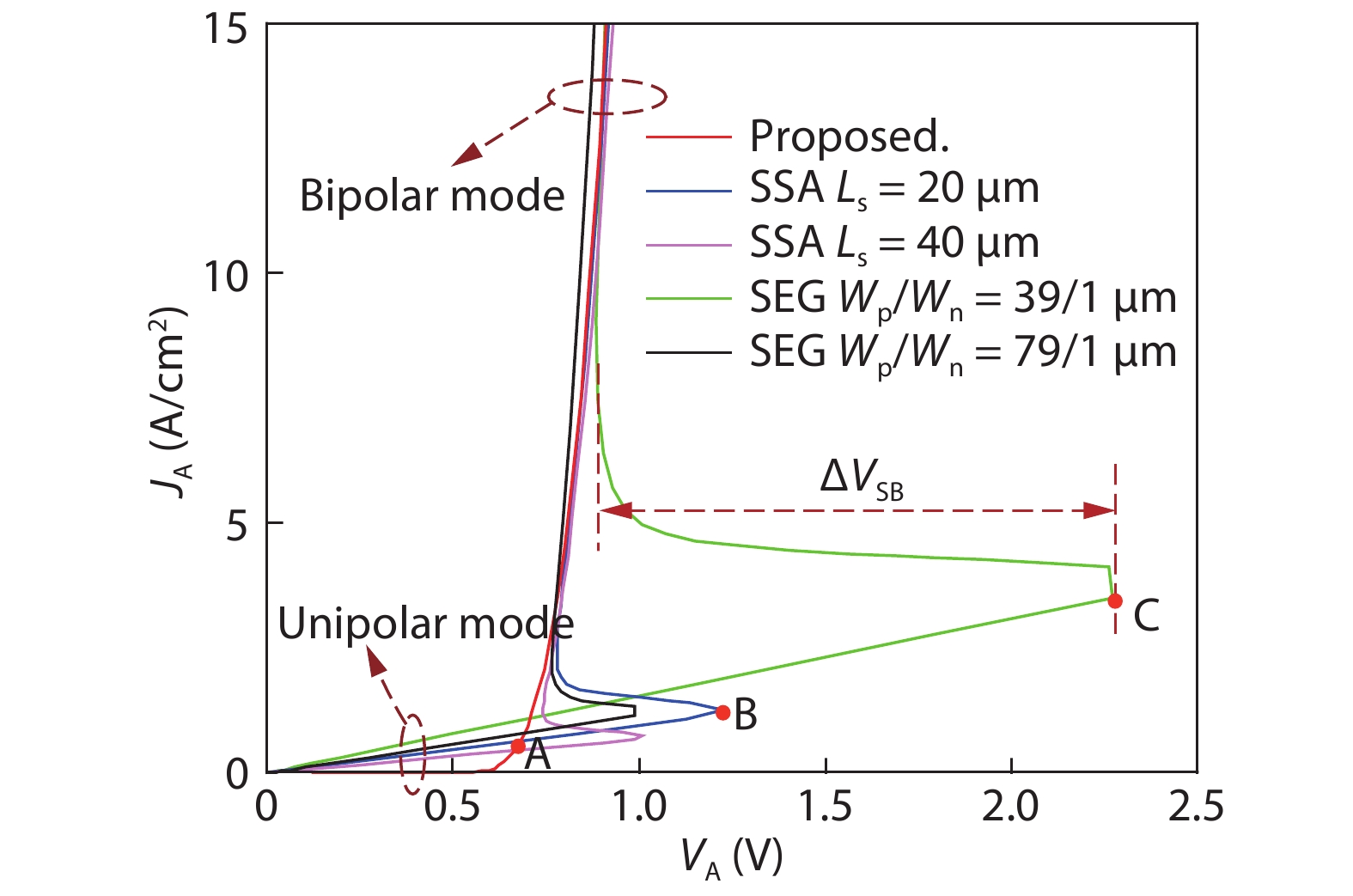

Modeling MOS snapback and parasitic bipolar action for circuit-level ESD and high current simulations | Semantic Scholar

Bipolar effects in snapback mechanism in advanced n-FET transistors under high current stress conditions - IOPscience

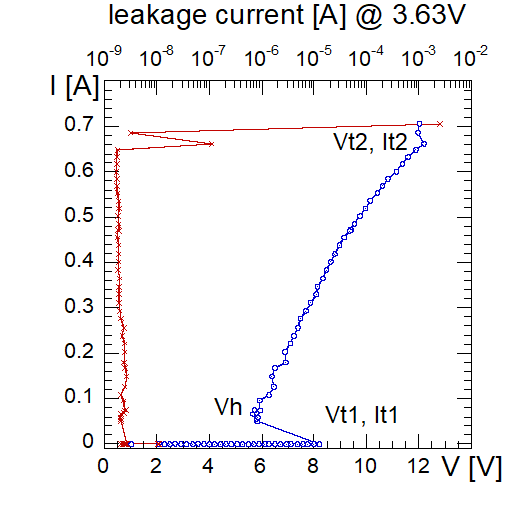

Snapback I-V curves and leakage currents of HV nLDMOSs with embedded... | Download Scientific Diagram

Figure 3 from A Study of Snapback and Parasitic Bipolar Action for ESD NMOS Modeling | Semantic Scholar

PDF) Snapback and Postsnapback Saturation of Pseudomorphic High-Electron Mobility Transistor Subject to Transient Overstress | Javier Salcedo - Academia.edu